SHY-FEC: Shaped Hybrid Forward Error Correction

This project studies the technical feasibility of our previously-introduced hybrid decoding and low-complexity shaping algorithms based on hardware implementations.

Duration

January 2021 - December 2022Project Manager

Project Related Publications

-

Yunus Can Gültekin,Frans M.J. Willems,Alex Alvarado

Band-ESS

(2023) -

Yunus Can Gültekin,Olga Vassilieva,Inwoong Kim,Paparao Palacharla,Chigo Okonkwo,Alex Alvarado

On Optimum Enumerative Sphere Shaping Blocklength at Different Symbol Rates for the Nonlinear Fiber Channel

(2022) -

Yunus Can Gültekin,Frans M.J. Willems,Alex Alvarado

Log-CCDM: Distribution Matching via Multiplication-free Arithmetic Coding

(2022) -

Yunus Can Gültekin,Alex Alvarado

Probabilistic Constellation Shaping Algorithms: Performance vs. Complexity Trade-offs

(2022) -

Alex Alvarado,Kaiquan Wu,Alexios Balatsoukas-Stimming

Reducing the Error Floor of the Sign-Preserving Min-Sum LDPC Decoder via Message Weighting of Low-Degree Variable Nodes

arXiv (2022)

Our Partners

Researchers involved in this project

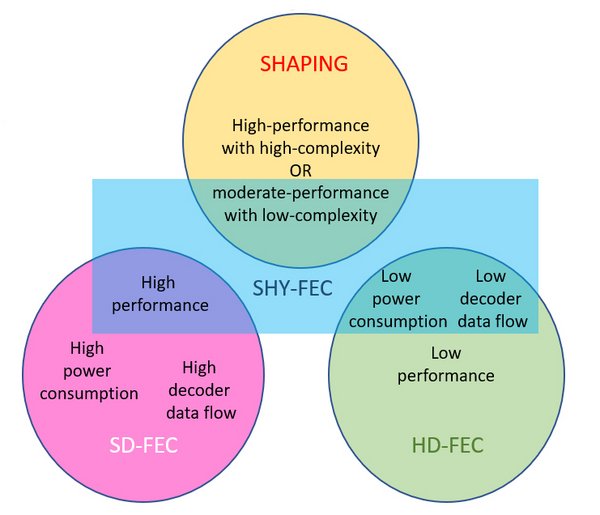

High-performance, low-power-consumption coded modulation techniques are crucial for next-generation optical and wireless communications. These requirements cannot be met at the same time with hard-decision or soft-decision forward error correction (FEC) codes. The EU-funded SHY-FEC project is proposing a breakthrough scheme that combines the high-performance property of soft-decision decoding and low-power-consumption property of hard-decision decoding. This hybrid FEC decoding structure combined with low-complexity constellation shaping will be a very attractive solution for high-speed communications, both for wireless and fibre-optic communication systems. The ultimate goal is to use this new approach to achieve comparable performance to the state-of-the-art soft-decision FEC codes, but with at least one order of magnitude lower energy consumption.

SHY-FEC is financed by the European Research Council Proof of Concept (ERC-PoC) funding, connected to the FUN-NOTCH project.

Optical fibers transport the majority of the IP traffic around the world. Over the last years, we have seen an explosive increase of data rates in fibre optics. For instance, in the short-haul domain, the traffic between data centers experienced a 400% growth from 2016 to 2021. This growth is a challenge not only to the technology demands but also to energy consumption. A single state-of-the-art optical transponder can reach a total power consumption of 700W (≈291pJ/bit). Applying Soft-Decision Forward Error Correction (SD-FEC) decoders would be superior in such multi-gigabit per second systems, but their power consumption is up to two orders of magnitude higher (hundreds of pJ/bit) than Hard-Decision Forward Error Correction (HD-FEC) decoders. However, choosing the technology with better energy efficiency comes with a cost: HD-FEC decoders entail a significant performance loss, which will prevent the use of HD-FEC decoders in ultra high-speed fiber optics. More broadly, such drawbacks will also make HD-FEC decoders impractical for beyond 5G mobile communications and future wireless local area network (WiFi-like) standards. In order not to increase future high-speed communication systems’ power consumption further, the error correction algorithms needs to be replaced with completely new approaches.

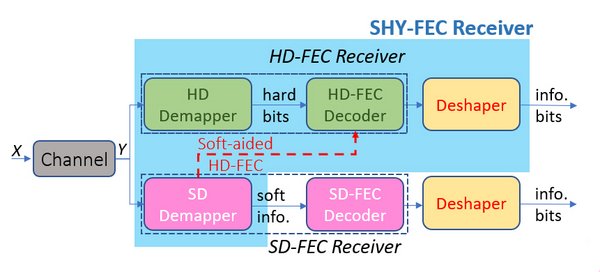

Recently, we made an innovation in tackling the challenge above, by combining high-performance SD-FEC and low-power HD-FEC in a hybrid FEC system (HY-FEC, see Fig. 1). The core structure of our proposed HY-FEC is similar to standard HD-FEC (see Fig. 2), and soft values are only used to improve the overall performance, making HY- FEC hardware friendly from an algorithmic level perspective. In particular, we have demonstrated that our approach is able to close the performance gap between SD-FEC and HD-FEC, but with at least one order of magnitude lower energy consumption than that of SD-FEC.

Furthermore, we have recently also discovered that with approximately-realised constellation shaping (SH) techniques applied to high-order constellations, higher data rates than that of systems without shaping can be attained with low-complexity (LC). In addition, we showed that LC-SH can be optimised for high-speed optical communications and devised an intellectual-property (IP)-protected algorithm for this purpose. We believe that the combination of LC-SH and HY-FEC with modest power consumption is the best solution for future high-speed communication systems. This combination forms the core of this project (see Fig. 1).

This project aims at establishing technical feasibility of our IP-protected algorithmic approaches which we previously introduced. The feasibility will be based on hardware implementations and thorough testing. Our ultimate goal is to obtain performance levels using SHY-FEC similar to those using traditional SD-FEC architectures without shaping, but with at least one order of magnitude lower energy consumption.