Research Profile

Important for our research are data converters based on sigma-delta modulation (SDM). We are working on the improvement of smart SDMs by applying our new limit-cycle theory to optimally correct their loop filters, their feedback DA converters and for stability estimation. We found new incremental methods, including a new decoding technique for highly accurate DC sensing with SDMs. In parallel we do research on ultra-high-speed SDM AD converters, using novel architectures that significantly relax the design requirements for meta-stability errors, for excess loop delay and for DAC jitter.

We derive and implement very high-speed high-resolution AD converter architectures, using a novel parallel sampling technique, exploiting information about the input signal distribution function.

Meet some of our Researchers

Recent Publications

Our most recent peer reviewed publications

-

Daan Rosenmuller,Bas van de Ven,Kostas Doris,Georgi I. Radulov,M.K. Matters-Kammerer,Erwin Janssen

The Impact of Transceiver Nonlinearity in PMCW Radar using Polyphase coded Sequences

(2023) -

Georgi I. Radulov,Ramiro Serra,A.A. Basten,Cecilia Martinez

Qualitative Assessment Guidelines for MSc Graduation Projects in Electrical Engineering

(2023) -

V. Vidojkovic,D. Milosevic,K. Ding,R. van Dommele,J. Holmstedt,C. van Puijenbroek,R. Schalk,Y. Hou,I. Zivkovic,G. Radulov

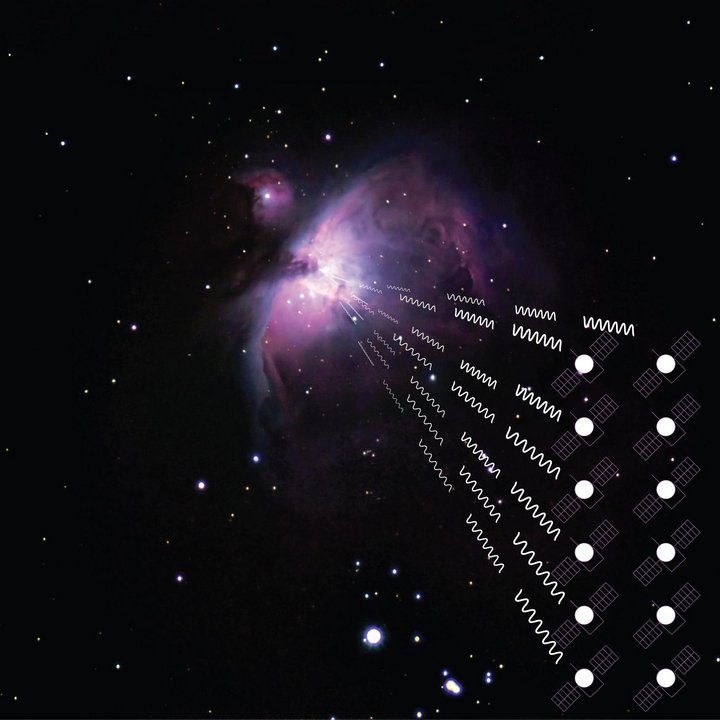

RF and mm-Wave Systems and Circuits for Communications and Sensing

(2023) -

Qilong Liu,Lucien J. Breems,Shagun Bajoria,Muhammed Bolatkale,Robert Rutten,Georgi Radulov

A 158-mW 360-MHz BW 68-dB DR Continuous-Time 1-1-1 Filtering MASH ADC in 40-nm CMOS

IEEE Journal of Solid-State Circuits (2022) -

Bas van de Ven,Daan Rosenmuller,Erwin Janssen,Kostas Doris,Georgi Radulov,Marion Matters-Kammerer

Mapping Error Reduction Methods for Polyphase Codes Generated by Quadrature Architectures

(2022)

Contact

-

Visiting address

Groene Loper 19Flux5612 AP EindhovenNetherlands -

Visiting address

Groene Loper 19Flux5612 AP EindhovenNetherlands -

Postal address

P.O. Box 513Department of Electrical Engineering5600 MB EindhovenNetherlands -

Secretary